Timing Paths

In today’s discussion, we

are only going to discuss timing paths of the design and here we go……………….

While analyzing the

timing of design, the STA tool breaks design into a number of paths and

calculate the delay along each path. Then, tool checks timing violation for

those paths which are not meet timing constraints.

While starting actual

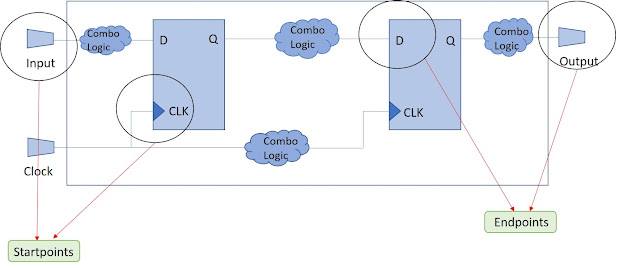

timing analysis for the paths, the STA tool determines the Startpoint and

Endpoint of the design.

Startpoints

- Input port of the design (other than clock port)

- Input clock pin of the sequential cell

Endpoints

- Output port of the design (other than clock port)

- Input data pin of the sequential cell

|

| Figure: Startpoints and Endpoints of the Design |

Once the STA tool determines

the startpoint and endpoint, then actually the analysis of timing paths starts.

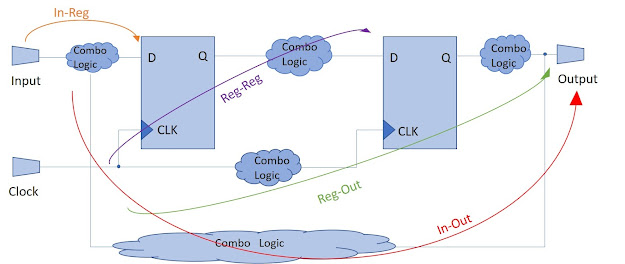

Timing Paths:

- In-to-Reg path:

From input port to D pin of sequential cell

- Reg-to-Reg path:

From sequential cell to sequential cell (from common clock network of launch

clock of the flip flop to D pin of capture Flip flop)

- Reg-to-Out path:

From sequential cell to the output port (from common clock network of launch

clock flip flop to output port)

- In-to-Out path:

From input to output port

Comments

Post a Comment

If you any doubt, please let me know