Terminologies of STA

In STA, there are a number of terms, we are

going to use while discussing STA concepts. That’s why we have to familiar with

those terms.

Clock

The timing signal oscillates between a

high and a low state. It is used to coordinate the actions of the digital

circuit. It is also called as a clock period. It consists of pulse width high

and low.

Frequency

The number of times clock repeats itself

in a second is called frequency.

F= 1/T

Duty cycle

The percentage of clock period for which

clock stays high is called a duty cycle.

D = (TON/T)/100

Transition or Slew

The time taken by the signal to change its

state (low to high or vice-versa) is called as transition time or slew. It has

two types - rise time and fall time.

Rise Time or Rise Slew (Tr)

The time taken by the signal to rise from

10% to 90% (or 20 to 70%) of its peak level (VDD) is called a rise time or rise

slew.

Fall Time or Fall Slew (Tf)

The time taken by the signal to fall from 90%

to 10% (or 70 to 20%) of its peak level (VDD) is called as fall time or fall

slew.

Delay

The time taken by the signal to propagate

from one point to another point is called a delay. There are two types of delay

cell delay and net delay.

Cell Delay

The time taken by the signal to propagate through

the cell is called as cell delay or propagation delay or gate delay.

|

| Figure: Propagation Delay* |

Net delay or flight delay

The delay due to the parasitic of a net is

called net delay or interconnect delay.

Intrinsic Delay

It is minimum delay offered by the gate

for zero load at the output and near the zero slew at the input.

Setup Time

The time interval for which data remains

stable before the arrival of an active clock edge.

Hold Time

The time interval for which data remains

stable after the arrival of an active clock edge.

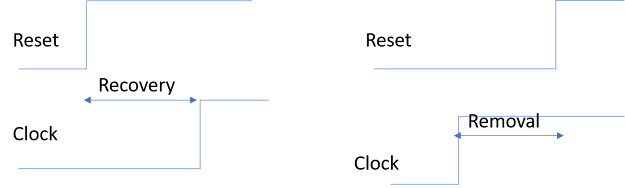

Recovery Time

It is the minimum amount of time required

between the release of an asynchronous signal from the active state to the next

active clock edge.

Removal Time

It is the minimum amount of time between

an active lock edge and the release of an asynchronous control signal.

Timing Arc

It represents the timing relationship between

two pins of the cell.

Critical Path

The path that fails to meet the timing constraints

of the design is called a critical path.

Arrival Time

The time taken by the signal to reach a

certain point is known as arrival time.

Required Time

The time available for the signal to reach a certain

point is known as required time.

Slack

The difference between arrival time and required

time is called slack.

Clock Path or Capture Path

The path starting from the common point of

clock network to clock pin of capturing sequential cell is called a clock path.

Data Path or Lunch Path

The path starting from the common point of

clock network to the data pin of capturing sequential cell is called a clock

path.

|

| Figure: Clock Path and Data Path* |

Clock Latency

The time taken by the signal from clock

source to clock pin of the sequence of cell is called as clock latency.

Source Latency

The time taken by the signal from clock

source to clock definition port is called as source latency.

Network Latency or Insertion Delay

The time taken by the signal from clock definition

port to clock pin of sequence of cell is called as network latency.

|

| Figure: Clock Latency* |

Clock Skew

The delay difference of clock paths

between two sequential cells is called clock skew.

Positive Clock Skew

The skew that occurs when the clock reaches

the captured cell later than the launch cell is called positive clock skew.

Negative Clock Skew

The skew that occurs when the clock reaches

the captured cell earlier than the launch cell is called negtive clock skew.

Synchronous Clocks

The clocks are said to be synchronous when

clocks have same source and have a fixed phase relationship.

Asynchronous Clocks

The clocks are said to be asynchronous

when clocks may or may have same source and have not fixed phase relationship.

Exclusive Clocks

Two clocks are said to be exclusive if and

only if one of them is active at a given time.

Logically Exclusive Clocks

Two clocks are said to be logically exclusive

if only one clock is active at a given time in block or chip but other clocks

are also activated or deactivate somewhere in the block of the chip.

Physically Exclusive Clocks

Two clocks are said to be physically exclusive

if only one clock is active in an entire chip at a given time. For example, when

the functional clock is active in the chip while the scan clock is not active.

Signal Integrity

It is a set of measures that define the

quality of the electrical signal.

Crosstalk

It is a phenomenon by which electrical signal

transmitted net creates an undesirable effect on its neighbouring net due to

coupling capacitance.

We will discuss these terms again in their

respective topic.

At this note of discussion, we wrapped up

this and we will meet soon with the new concept of STA. Thank you. Have a nice

day!!

Comments

Post a Comment

If you any doubt, please let me know