Setup Time & Hold Time

Today,

we are going to discuss the setup and hold time of flip flop. But before that, we have to understand the

functioning of flip flop itself and here we go……….

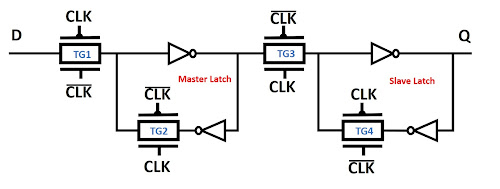

Setup and hold time are very much contributed to the timing path. Whether flipflop is able to capture the data or not? Before talking about setup and hold time, we have to understand the working of a flip flop. Then, we discuss what is setup and hold time. As we have seen flip flops are made from NAND or NOR gates. But in reality, it is made of CMOS. More specifically, CMOS transmission gate.

|

| Figure: CMOS Transmission Gate Flip-Flop |

Flip-Flop Operation

Flip flop made of CMOS consists of Master and slave latch which are made from CMOS Transmission Gate.

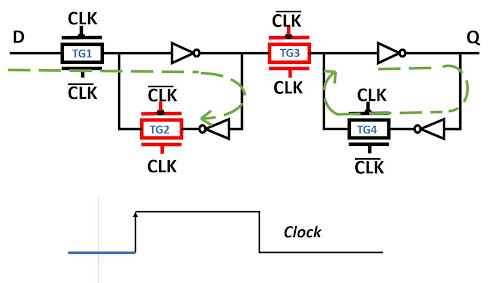

When CLK = 0, TG1 and TG4 are ON. Data from D pin is passing through the series of inverter and data locked, and waiting for TG2 to be ON, so that it can pass through Q. When TG4 is ON, slave latch sent the previous state value to D pin capture flip flop through Q.

|

| Figure: TG1 and TG4 ON at CLK = 0 |

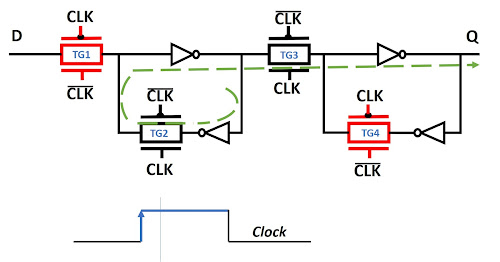

When CLK = 1, TG2 and TG3 are ON. Locked value of D is passed to Q through TG3 and the same value of the present state is stored in the slave latch. It will release when TG4 will ON at CLK = 0.

|

| Figure: TG2 and TG3 ON at CLK = 1 |

The way of working of flip flop determine the setup and hold value of flip flop.

Setup Time

In flip flop, data from D pin takes a finite time to reach TG2. When the clock makes rise transition, TG1 is OFF and TG2 is ON and latching data. It means that the time taken by data signal to reach from D pin to TG2 contributes the setup time.

To understand we see it through the values. Consider, time taken by data signal from D pin to TG2 (TDS) is 200ps and time taken by clock to set CLK and C̅L̅K̅ (TCS) is 70ps, then Setup Time = TDS - TCS = 200-70 = 140ps. Therefore, the setup time of the flip flop is 0.14ns

Hold Time

At clock edge of flip flop, data from launch flip flop, sent by slave latch, must stable till TG1 ON. Once data captured by the master latch of flip flop, then there will be not metastability. There is a finite delay between clock reaches to the set CLK and C̅L̅K̅ and turned them off (TCS). The delay of the data signal from D of capture flip flop to TG1, which is very small, (TDS). These two parameters determine the hold time of flip flop.

To understand this, we used the same values as we used before for TDS and TCS. Here the value of TCS is more than TDS. Then, the hold time = TCS - TDS = 70-200 = -140ps. Therefore, the hold time of the flip flop is -0.14ns.

On conclusion of the above, it is important to note that the value of setup time is always positive, and hold time may be positive, negative or zero.

But setup time also can be a negative value. Here another important thing is that summation of setup time and hold time must be positive ALWAYS !!

At

this note of discussion, we wrapped up the topic and we will meet soon with a new

topic of STA. Thank you. Have a nice day!!

Comments

Post a Comment

If you any doubt, please let me know